### Génération de tests basés sur les modèles pour des systèmes sur puce avec cohérence de caches

Massimo Zendri & Abderahman Kriouile

STMicroelectronics DCG / IP dev / FVS

# Model based test generation for cache coherent Systems On Chips

Massimo Zendri & Abderahman Kriouile

STMicroelectronics DCG / IP dev / FVS

Our MEMS & Sensors are augmenting the consumer experience

Our automotive products are making driving safer, greener and more entertaining

life.augmented Ø

Our smart power products are allowing our mobile products to operate longer and making more of our energy resources

#### Where you find us

Our digital consumer products are powering the augmented digital lifestyle

Our Microcontrollers are everywhere making everything smarter and more secure

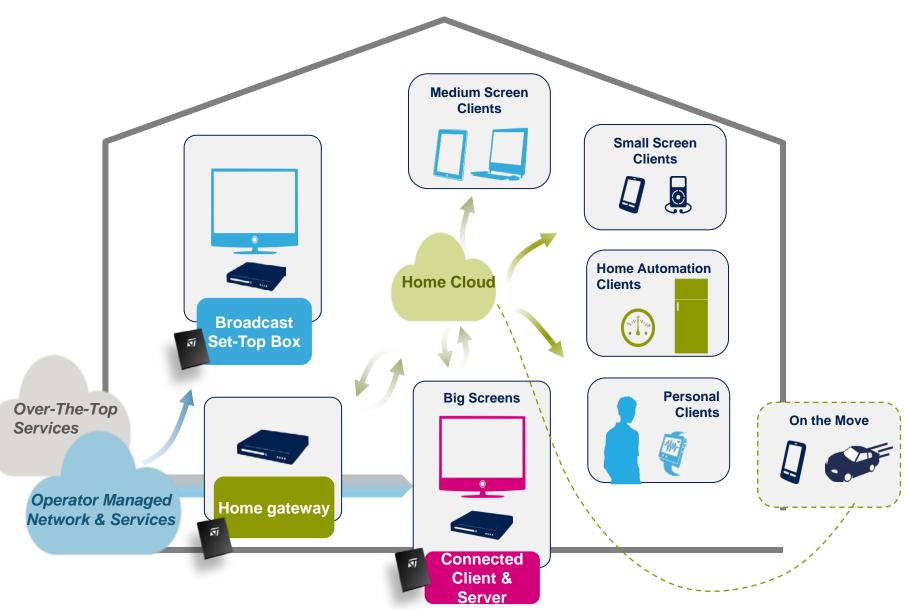

### Towards the Home Cloud

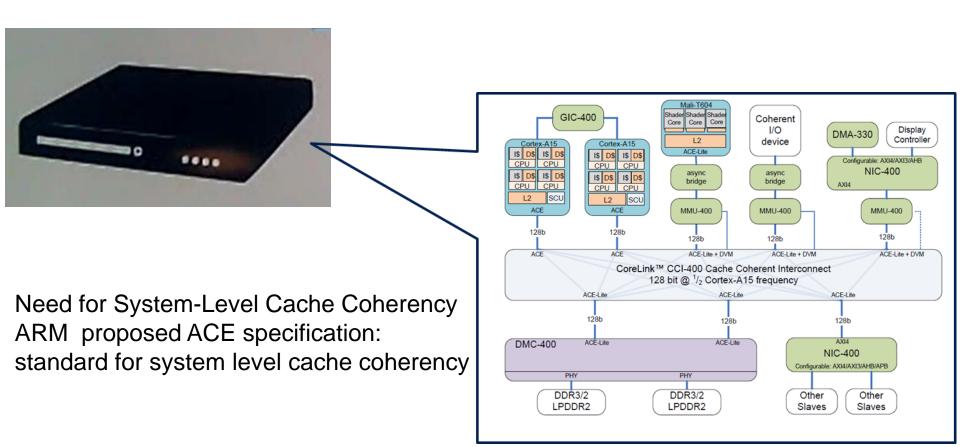

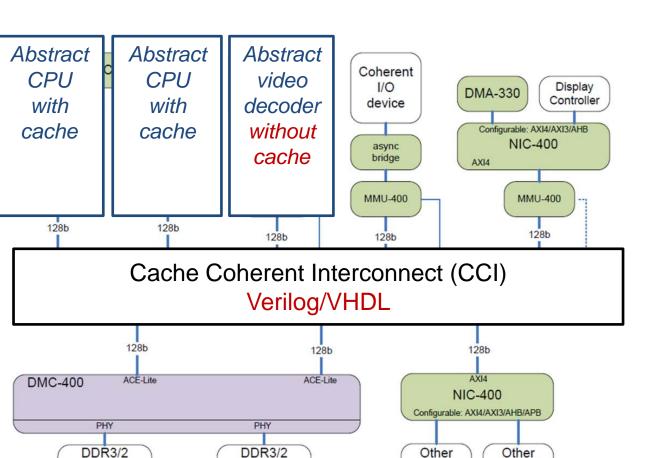

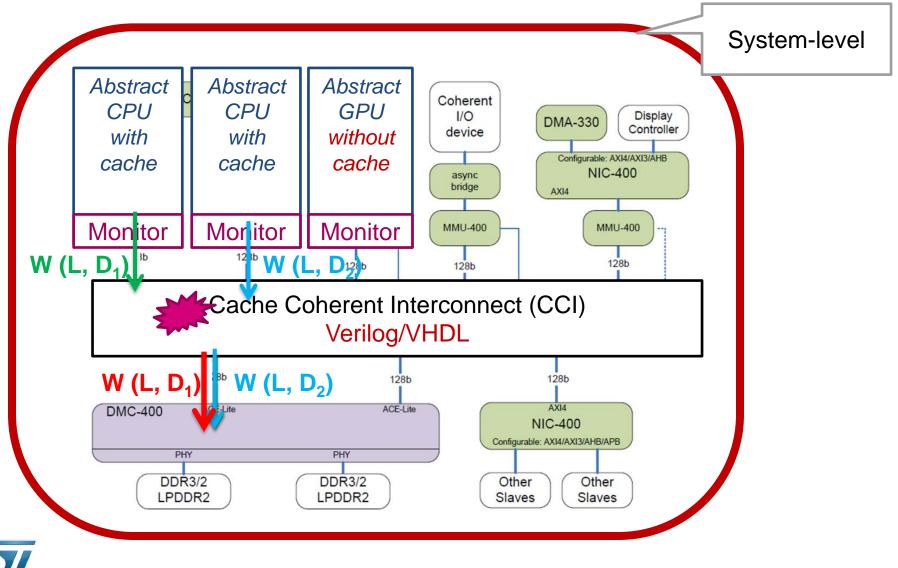

# Heterogeneous System-on-Chip (SoC)

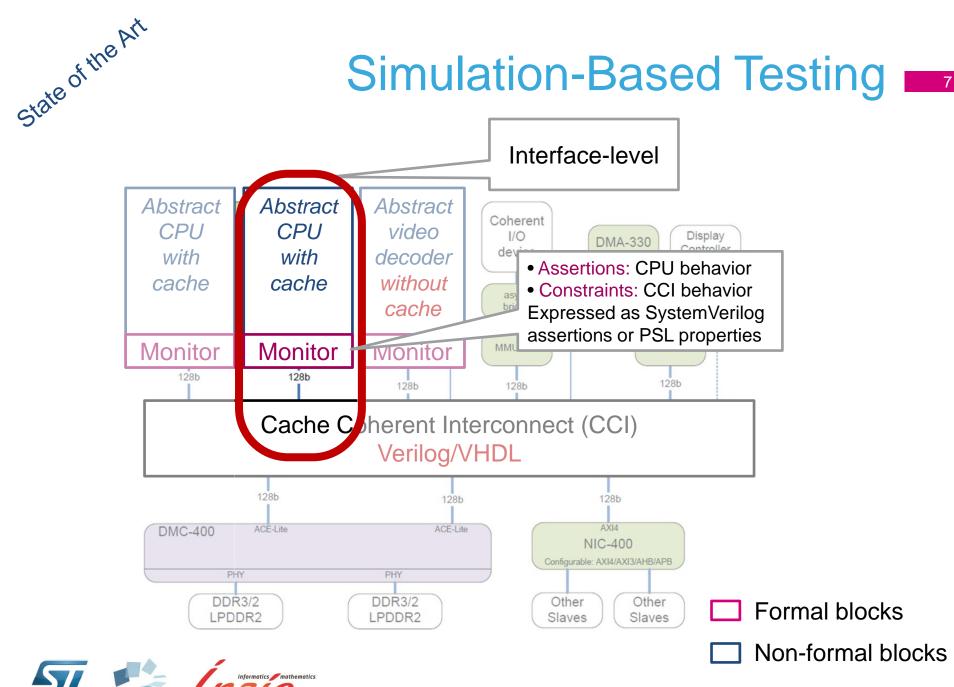

# **Simulation-Based Testing**

LPDDR2

Slaves

Slaves

LPDDR2

life.auamented

#### Model Checking (without running any test)

- Applying restrictions for more exploration

- Limitation due to state-space explosion problem

# HW Model Based Test Generator

State of the Art

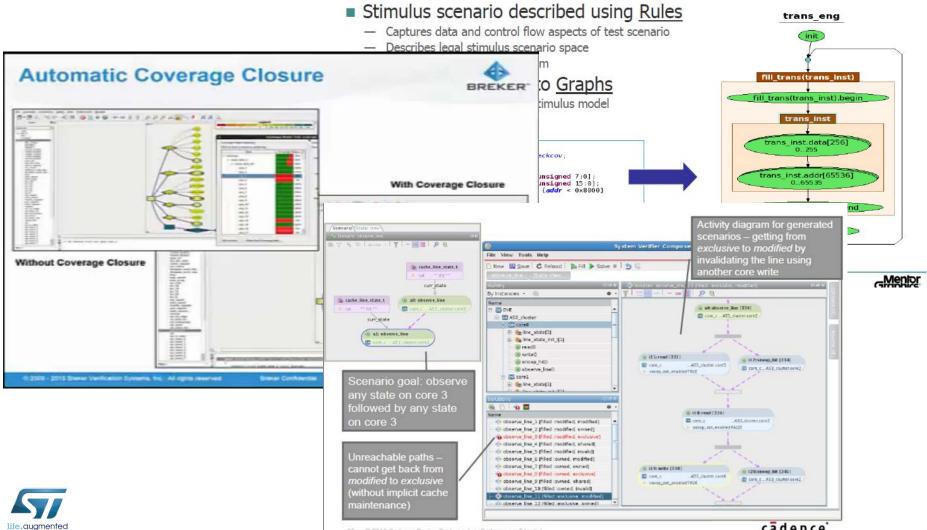

#### **Graph-Based Stimulus Description**

cādence

### Need for System-Level Verification 10

life, gugmented

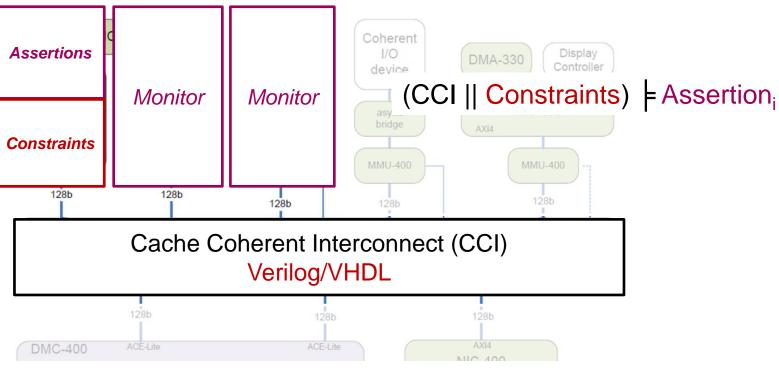

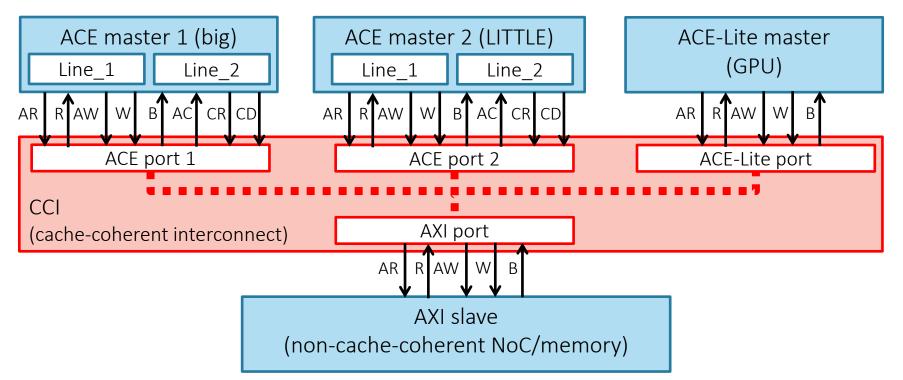

### Formal Model of an ACE-based SoC

- Interface transfers modeled by rendezvous

- 3400 lines of LNT code derived from ACE specification

- Parametric: #masters, forbidden ACE transactions, ...

- [Kriouile-Serwe-13] Formal Analysis of the ACE Specification for Cache Coherent Systems-on-Chip, FMICS, LNCS 8187, 2013

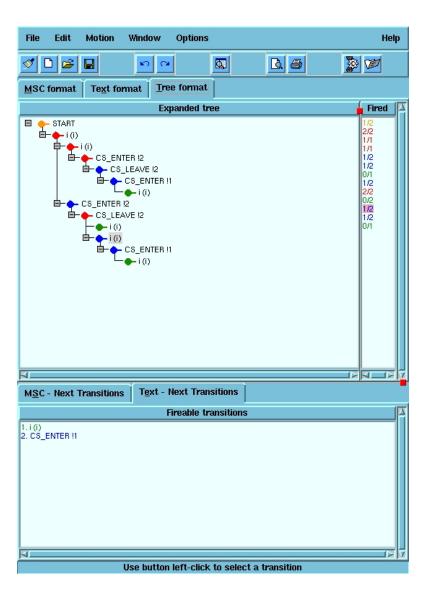

# CADP: OCIS (Open/Cæsar Interactive Simulator)

- language-independent

- tree-like scenarios

- save/load scenarios

- source code access

- dynamic recompile

12

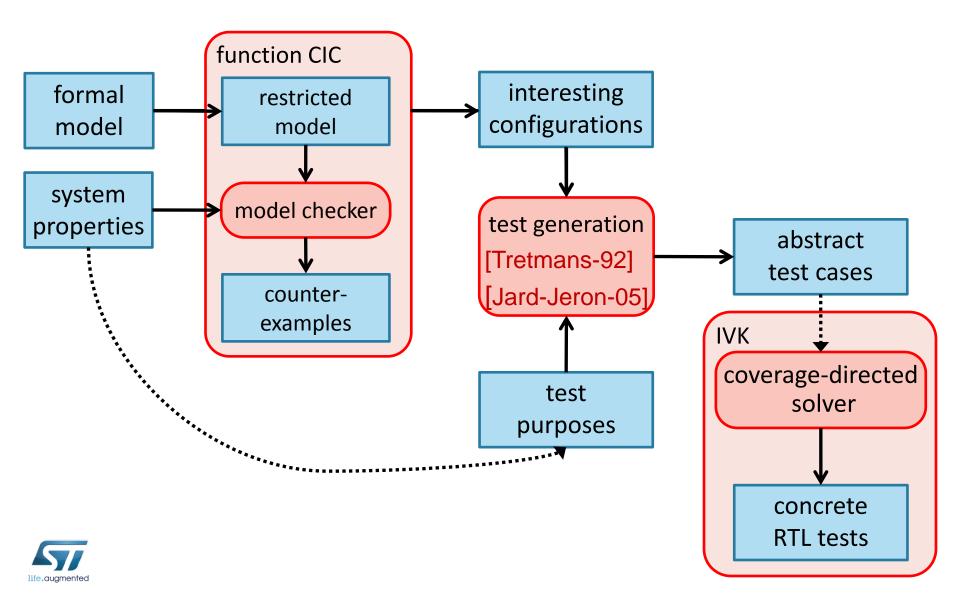

#### Generation of System-Level Test Cases 13

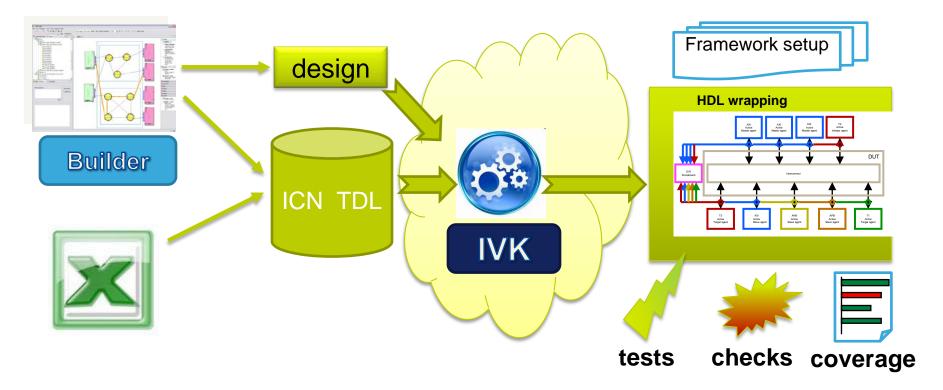

#### IVK (Interconnect Verification Kit): Automated Interconnect Testbench Generation

#### Inputs

Architectural description (TDL) either generated by interconnect designers GUI or through Excel flow

#### Outputs

Full Verification Environment, including sequences and coverage models

# Several Kinds of Derived Tests

#### 39 + 3 generated CTGs (Complete Test Graphs)

| prop.     | masters    | global CTG |            | extr.   | nb. of          | . of largest CTG |           | smallest CTG |        | $\operatorname{extr.}$ |

|-----------|------------|------------|------------|---------|-----------------|------------------|-----------|--------------|--------|------------------------|

|           |            | states     | trans.     | time    | $\mathrm{CTGs}$ | states           | trans.    | states       | trans. | $\operatorname{time}$  |

| $arphi_3$ | 2ACE       | 6,402      | $14,\!323$ | >1/2 y  | 18              | 903              | $1,\!957$ | 274          | 543    | $\simeq 7 h$           |

| $arphi_5$ | 2ACE       | $23,\!032$ | 48,543     | >1/2 y  | 14              | 462              | 888       | 59           | 107    | <1h                    |

|           | 1ACE/1Lite | 2,815      | $7,\!071$  | > 1/2 y | 7               | 193              | 394       | 59           | 107    | <1h                    |

#### 296 simple system-level tests

- for each correct initial state with two masters possibly sharing a memory line, initiate all permitted transitions

- check correct behavior of the Cache Coherent Interconnect (e.g., generation of corresponding snoops)

10 sequence tests to recreate counter-examples

- concurrency between transactions

- conditioned by response of the Cache Coherent Interconnect

- 300 IVK tests generated

- Many problems identified on the verification environment (VIP components)

- System level assertions to check system behavior

- 100% coverage of system level assertions

- Reproduction of 1 suspected architectural issue

- Used on 2 currently developed products (codenamed Orly3 and Barcelona)